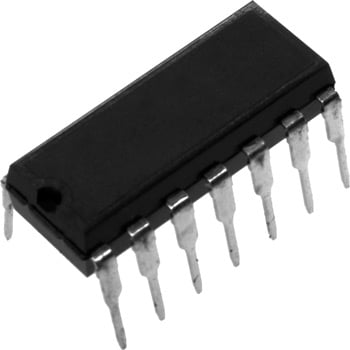

Dual J-K Negative Edge Triggered Flip/Flop

74LS114

$1.86

| QTY | Price |

|---|---|

| 1 | $1.86 |

| 10 | $1.67 |

| 25 | $1.51 |

Description

This device has two independent J-K negative-edge-triggered flip-flop. A low level at the preset (PRE) or clear (CLR) inputs sets or resets the outputs. This is regardless of the levels of the other inputs.

When PRE and CLR are inactive (high), data at the J and K inputs that meet the setup-time requirements is transferred to the outputs on the clock pulse's negative-going edge (CLK). Clock triggering occurs at a voltage level and is unrelated to the fall time of the clock pulse.

Following the hold-time interval, you can change data at the J and K inputs without affecting the levels at the outputs. By tying J and K high, these versatile flip-flops can function as toggle flip-flops.

Specifications

Pins

14

Operating Temperature

0 - 70°C

Supply Voltage

5 V

Terminal Finsh

Tin/Lead (Sn/Pb)

Dimensions

Terminal Pitch

2.54 mm

You Might Also Like

All prices are in Australian Dollars and include GST. GST will be removed from your order if you are ordering from outside Australia.

Products may differ from pictured.

All trademarks and trade names are the properties of their respective owners. Wiltronics disclaims any proprietary interest in trademarks and trade names other than its own.